lab06 : Simulation of MIPS R-Type Datapath

| num | ready? | description | assigned | due |

|---|---|---|---|---|

| lab06 | true | Simulation of MIPS R-Type Datapath | Fri 02/21 08:00AM | Wed 02/26 11:59PM |

Due Wednesday, Feb. 26th at 11:59 PM

Goals for This Week

By the time you have completed this work, you should be able to utilize pyrtl and Python to simulate common CPU hardware and design a basic R-Type instruction datapath.

Step by Step Instructions

Build a MIPS instruction decoder in PyRTL

You will be using the PyRTL library just like you did in lab03 and lab05.

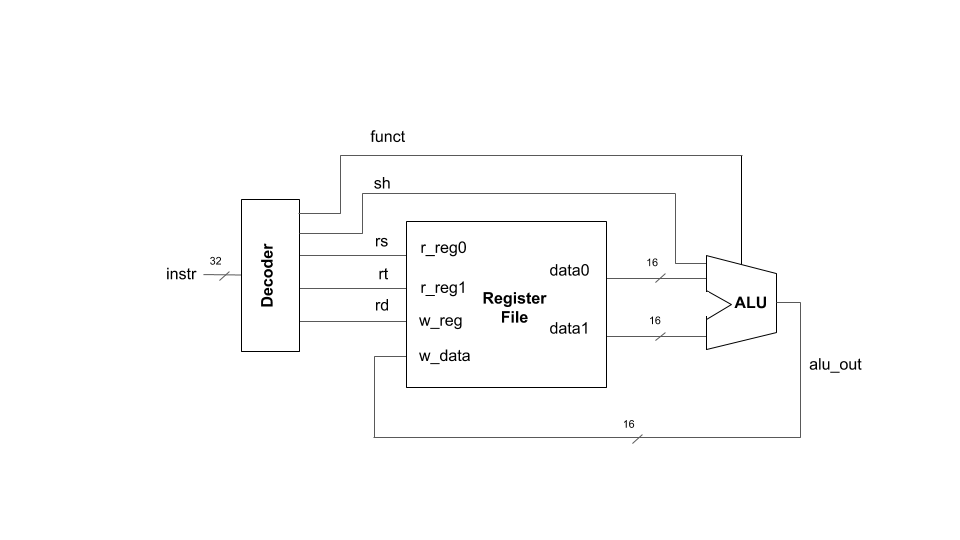

The goal of this lab is to build (part of) the datapath of a single-cycle 32 bit MIPS processor using PyRTL. Here’s what you need to know:

- The instructions that your ALU should support are: ADD, SUB, AND, OR, XOR, SLL, SRL, SRA, and SLT (that is to say, R-Type instructions).

- Part of this datapath is the register file which must have 32 registers (just like MIPS).

- To implement the desired register file use PyRTL’s MemBlock.

- The machine will fetch a new instruction every cycle.

- What you are working with is a simple, non-pipelined design in which everything happens in one cycle (i.e. don’t worry about cycle time).

- Make sure that you name your “wires” as indicated below; otherwise, the autograder will not work.

- Watch for clarifications from your lab TAs in lab or announced on Piazza.

See the block diagram below to help guide your work.

Submit your work to Gradescope (this will be set up by the weekend for your submissions and announced on Piazza).

Copyright 2020, Ziad Matni, CS Dept, UC Santa Barbara. Permission to copy for non-commercial, non-profit, educational purposes granted, provided appropriate credit is given; all other rights reserved